Mostantól követi felhasználót

A felhasználó követése sikertelen.

Ez a felhasználó nem engedélyezte mások számára, hogy kövessék.

Ön már követi ezt a felhasználót.

Tagsági előfizetésével csak 0 követésre van lehetősége. Itt fejlesztheti tagságát.

Nem követi a továbbiakban felhasználót

A felhasználó követésének kikapcsolása során hiba lépett fel.

Sikeresen ajánlotta felhasználót

A felhasználó ajánlása során hiba lépett fel.

Valami hiba történt. Kérjük, frissítse az oldalt és próbálja újra.

E-mail cím hitelesítése sikeres.

singapore,

singapore

Itt jelenleg ennyi az idő: 6:52 de.

Ekkor csatlakozott: augusztus 10, 2014

30

ajánlás

Loi L.

@loi09dt1

6,9

6,9

84%

84%

singapore,

singapore

99%

Teljesített megbízások

93%

Költségvetésen belül

97%

Határidőn belül

14%

Ismételt megbízási arány

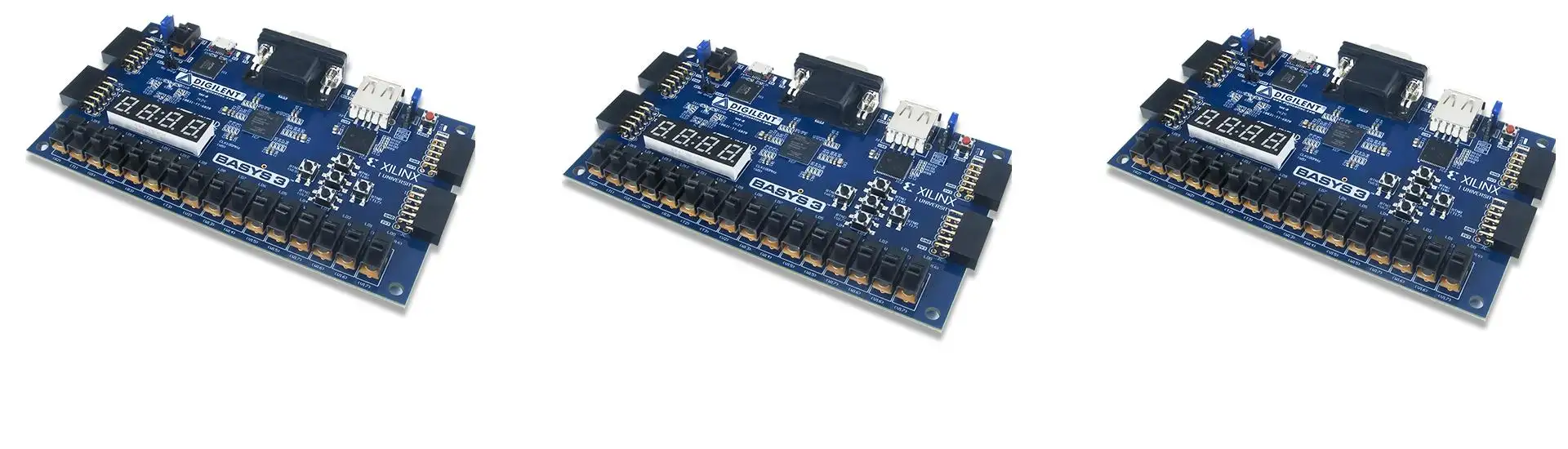

FPGA/Verilog/VHDL Expert

Keresse Loi L. felhasználót a munkájával kapcsolatban

Jelentkezzen be, hogy chaten keresztül megbeszélhessék a részleteket.

Portfólió

Portfólió

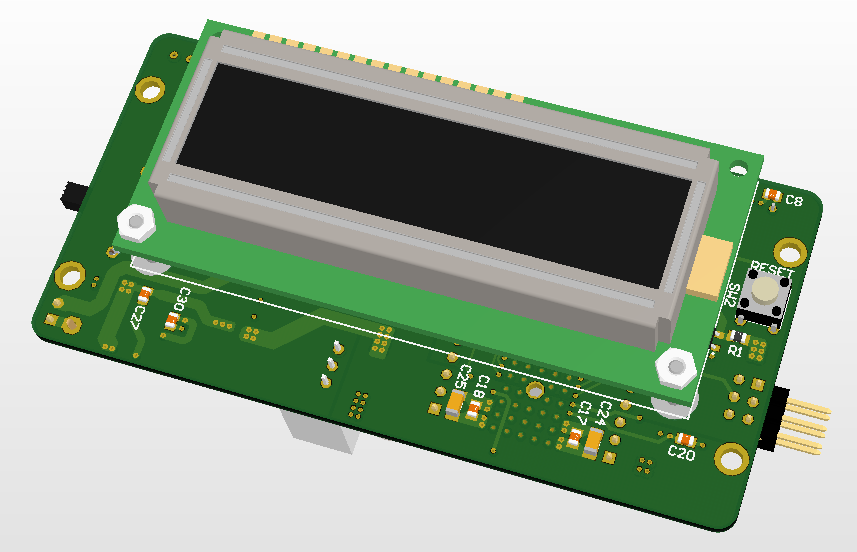

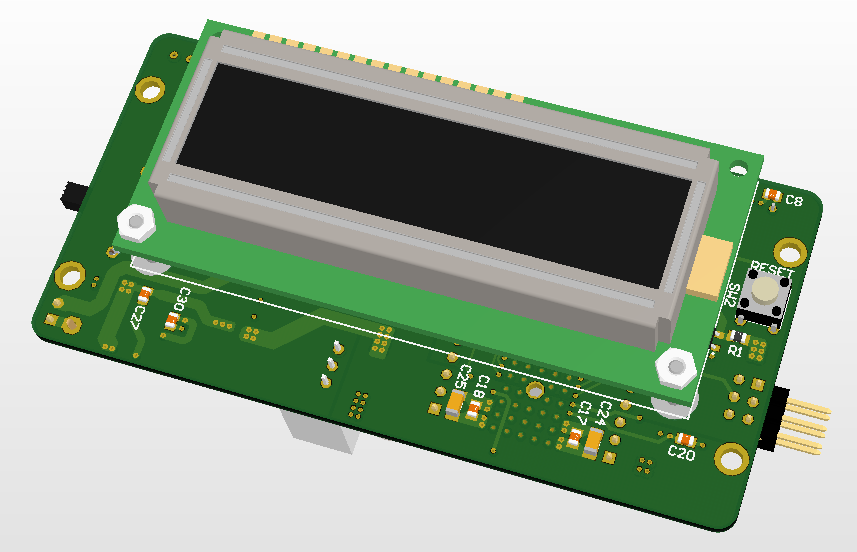

Quadcopter Controller Board

Quadcopter Controller Board

Magnet Controller using Android Apps - Shipped to US

Universal Remote + Camera + Wifi Module

Universal Remote + Camera + Wifi Module

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

4-Layers PCB Layout using Altium Designer

4-Layers PCB Layout using Altium Designer

RFID project

Quadcopter Controller Board

Quadcopter Controller Board

Magnet Controller using Android Apps - Shipped to US

Universal Remote + Camera + Wifi Module

Universal Remote + Camera + Wifi Module

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

4-Layers PCB Layout using Altium Designer

4-Layers PCB Layout using Altium Designer

RFID project

Értékelések

Változtatások elmentve

1 - 5 / 50+ értékelés látható

$270,00 USD

C Programming

Engineering

Verilog / VHDL

Electrical Engineering

FPGA

A

•

$70,00 CAD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

•

$200,00 CAD

Electronics

Verilog / VHDL

Electrical Engineering

Arduino

FPGA

G

•

$150,00 USD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

+1 további készség

J

•

$80,00 USD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

+1 további készség

J

•

Tapasztalat

FPGA/Verilog/VHDL Developers

jan. 2018 - Jelenleg

Founder of FPGA4student. An experienced FPGA/Verilog/VHDL Engineer with more than 6 years experience and hundreds of FPGA projects in Verilog/ VHDL, Digital Logic/Circuit/System Design in LogiSim/CEDAR, and MIPS Assembly.

Expertise: Xilinx ISE, Vivado, Quartus, Modelsim, Logisim, CEDAR, Qtspim, MARS, PSpice, Altium, OrCAD, Proteus, Arduino.

Founder

nov. 2016 - Jelenleg

FPGA4student where shares free FPGA/Verilog/VHDL source code/ projects/ tutorials with EEE students.

Also offering FPGA/Verilog/VHDL Design/ Tutoring/ Consulting Services.

Experienced FPGA/Verilog/VHDL Engineer

aug. 2014 - Jelenleg

An experienced FPGA/Verilog/VHDL engineer with more than 6 years experiences on FPGA Design using Verilog/ VHDL, digital logic design LogiSim, Circuit design, MIPS Assembly, etc.

Tanulmányok

IC Design Course

(1 év)

Bachelor of Engineering

(5 év)

Végzettségek

IC Design Course Completion

Synopsys

2014

IC Design Course using Synopsys Design Tools

Odon Vallet scholarship

Prof. Odon Vallet and "Meeting Vietnam" Organization

2013

Scholarship for best performed students in central region of Vietnam in 2013

Intel Vietnam Engineering scholarship

Intel Vietnam

2012

Scholarship for top engineering students at DUT in 2011 and 2012

Publikációk

A FPGA-Based Embedded Fingerprint Identification System

the 2014 National Conference on Electronics, Communications and Information Technology – REV-ECIT 2014

A FPGA-Based Embedded Fingerprint Identification System on the 2014 National Conference on Electronics, Communications and Information Technology – REV-ECIT 2014

A FPGA-Based Embedded Fingerprint Identification System

The University of Danang

A FPGA-Based Embedded Fingerprint Identification System

Keresse Loi L. felhasználót a munkájával kapcsolatban

Jelentkezzen be, hogy chaten keresztül megbeszélhessék a részleteket.

Hitelesítések

Képesítések

Kiemelt készségek

Hasonló szabadúszók keresése

Hasonló bemutatók böngészése

Meghívó sikeresen elküldve!

Köszönjük! E-mailben elküldtük a linket, melyen átveheti ajándék egyenlegét.

E-mailje elküldése során valami hiba történt. Kérjük, próbálja újra.

Előnézet betöltése

Hozzáférést adott a helymeghatározáshoz.

Belépési munkamenete lejárt, és kijelentkeztettük. Kérjük, lépjen be újra.